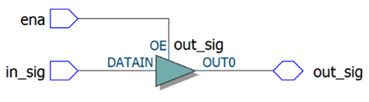

Для приведенной ниже структуры создайте описание на языке Verilog

Другие предметы Колледж Описание на языке Verilog теория дискретных устройств Verilog описание структуры колледж цифровые схемы логические элементы проектирование устройств программирование на Verilog дискретные устройства учебный проект

Для создания описания структуры на языке Verilog, необходимо сначала понять, какая именно структура подразумевается. Предположим, что речь идет о простом цифровом устройстве, например, о 4-битном сумматоре. Давайте рассмотрим, как можно описать такой сумматор на Verilog.

Шаги для создания описания 4-битного сумматора:

- Определение модуля: Начнем с объявления модуля. Модуль будет иметь 4 входа для двух 4-битных чисел и один выход для результата, а также один бит для переноса.

- Объявление входов и выходов: Укажем, какие порты будут входами и выходами модуля.

- Логика сумматора: Опишем логику суммирования с использованием операторов Verilog.

Теперь давайте перейдем к коду:

module four_bit_adder (

input [3:0] A, // Первое 4-битное число

input [3:0] B, // Второе 4-битное число

output [3:0] SUM, // Сумма

output COUT // Перенос

);

assign {COUT, SUM} = A + B; // Сложение двух 4-битных чисел

endmodule

Объяснение кода:

- module four_bit_adder: Это объявление модуля с именем four_bit_adder. Внутри него мы будем описывать поведение нашего сумматора.

- input [3:0] A, B: Здесь мы объявляем два 4-битных входных порта A и B. Они будут использоваться для передачи значений, которые мы хотим сложить.

- output [3:0] SUM: Это 4-битный выход, который будет хранить результат сложения.

- output COUT: Это выход для переноса, который будет указывать на наличие переноса из старшего разряда.

- assign {COUT, SUM} = A + B: Здесь происходит основное действие. Мы используем оператор сложения, который складывает два числа A и B, и результат сохраняется в переменные SUM и COUT. Мы используем фигурные скобки для объединения двух выходов в одно значение.

Таким образом, мы создали простой 4-битный сумматор на языке Verilog. Если у вас есть конкретная структура, которую нужно описать, пожалуйста, уточните, и я помогу вам с ее реализацией.