На языке Verilog создайте описание реверсивного N разрядного двоичного счетчика с параллельной загрузкой

Другие предметы Университет Проектирование цифровых схем на языке Verilog реверсивный двоичный счетчик Verilog параллельная загрузка N разрядный счетчик описание счетчика дискретные устройства цифровая логика

Создание реверсивного N-разрядного двоичного счетчика с параллельной загрузкой на языке Verilog требует понимания основных компонентов и принципов работы счетчиков. Давайте разберем, как это можно реализовать шаг за шагом.

Шаг 1: Определение параметров

Сначала определим параметр N, который будет указывать количество разрядов счетчика. Это можно сделать с помощью директивы `parameter`.

Шаг 2: Определение входов и выходов

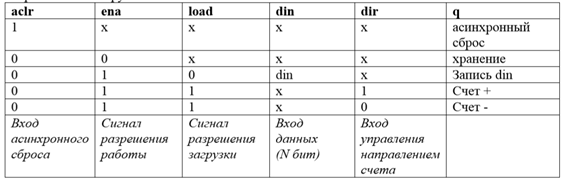

Счетчик будет иметь следующие входы и выходы:

- clk - тактовый сигнал

- reset - сигнал сброса

- load - сигнал для параллельной загрузки

- data - входные данные для загрузки (N бит)

- count - выходное значение счетчика (N бит)

Шаг 3: Определение внутреннего состояния

Создадим регистр для хранения текущего значения счетчика. Он будет иметь размер N бит.

Шаг 4: Описание логики работы

Счетчик должен работать следующим образом:

- При активном сигнале reset счетчик должен обнуляться.

- При активном сигнале load значение из входа data должно загружаться в счетчик.

- В противном случае, при каждом тактовом сигнале, значение должно уменьшаться на единицу.

Шаг 5: Код на Verilog

Теперь мы можем написать код для нашего реверсивного N-разрядного двоичного счетчика:

module reverse_counter #(parameter N = 4) (

input clk,

input reset,

input load,

input [N-1:0] data,

output reg [N-1:0] count

);

always @(posedge clk or posedge reset) begin

if (reset) begin

count <= 0; // Сброс счетчика

end else if (load) begin

count <= data; // Параллельная загрузка

end else begin

count <= count - 1; // Уменьшение счетчика

end

end

endmodule

Объяснение кода:

- Мы объявляем модуль reverse_counter с параметром N.

- Входы и выходы определены в заголовке модуля.

- В блоке always мы описываем поведение счетчика при положительном фронте тактового сигнала или при сбросе.

- Если сигнал reset активен, счетчик устанавливается в 0.

- Если активен сигнал load, счетчик загружает значение из data.

- В противном случае, значение счетчика уменьшается на 1.

Таким образом, мы создали реверсивный N-разрядный двоичный счетчик с параллельной загрузкой. Вы можете изменить значение N, чтобы получить счетчик с нужным количеством разрядов.